ANE405

# Bi-directional Data Transfer between MC68HC11 and MC6805L3 using SPI

by Richard Soja, Motorola, EKB

### INTRODUCTION

One of the most powerful features shared by a wide range of Motorola MCUs is the Serial Peripheral Interface (SPI). It is primarily designed to operate as a synchronous, 8-bit communication system and is implemented entirely with on-chip hardware. This frees the CPU for other tasks and ensures a minimum of software overhead associated with the SPI system.

The SPI is available in two basic forms:

- 1. Level 1 SPI implemented on the MC68HC11, HC05C4 MCUS,

- 2. Level 2 SPI implemented on the MC6805S2/S3/L3/L8 MCUs.

Note that the HCMOS family of MCUs only support level 1, while level 2 is implemented only on HMOS MCUs.

Though both levels of SPI can communicate easily with each other, level 2 has a number of additional capabilities, including asynchronous communication. This application note is aimed at describing a method of achieving synchronous communication between a level 1 and level 2 SPI, and details the subtle relevant differences in the on-chip implementation of each.

# **DESCRIPTION**

The two MCUs used in this application are the high performance MC68HC11 and the low cost MC6805L3.

Data is transferred between the MCUs on a single

bi-directional line, with the clock supplied on an additional line. Also, to ensure initial synchronisation between each MCU, a software handshake sequence is implemented on the same lines which provide the clock and data. This has the considerable advantage of minimising the number of lines between each MCU as additional control lines are not needed.

The handshake sequence is also necessary for two other reasons; the 6805L3 receive data register is unbuffered, and it is not possible for the 6805L3 to stop transmission of data from the 68HC11 by inhibiting the clock signal. The fact that the 6805L3 data register is unbuffered means that, if a handshake sequence was not implemented, new data could begin to get clocked in before the previous data were read. Also, the on-chip configuration of the 68HC11's SPI means that, if an attempt were made to slow down or stop its clock during transfer of a byte, there would be a resultant loss of synchronism between the transmitting and receiving MCUs.

The 68HC11 software is implemented as the clock master (i.e. it provides the clock output), while the 6805L3 is the clock slave. As there are no other clock masters or slaves in the system, software is kept to an absolute minimum. In fact the main transfer routine (XFER) for the 68HC11 is only 27 bytes long, while the 6805L3 uses only 30 bytes.

The other significant advantage of this implementation is that none of the 6805L3 timers are required for SPI operation, thus ensuring a minimal impact on any other application dependent tasks the MCU may be executing.

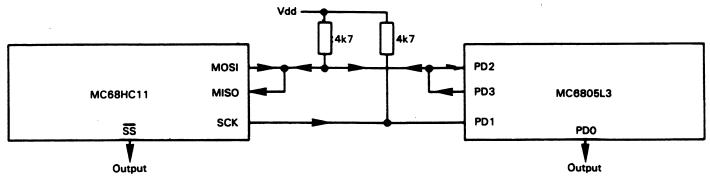

Figure 1. Hardware Implementation

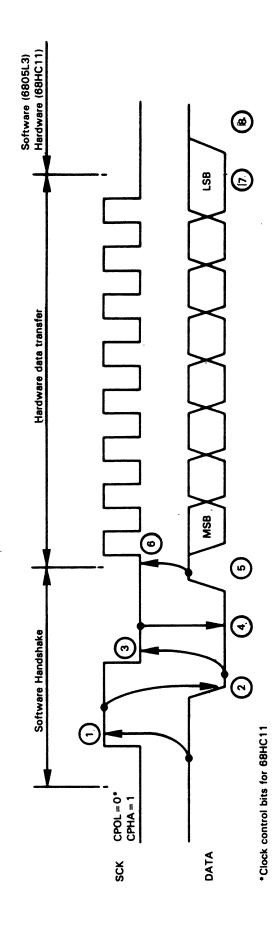

Figure 2. 68HC11-6805L3 SPI Timing

- Master releases clock line by disabling SPI.

- Slave clears data line by forcing o/p clamp on PD3.

(a)

Master clears clock line by enabling SPI.

**⊚ ₹**

- Once clock line goes low, slave stores data in SPI data register, sets its data DDR to correct state, and enables SPI.

- Slave releases data clamp.

ھ

Master starts SPI clock by storing data in SPI register.

(a) (b)

- Both master and slave detect end of transmission and read data from SPI register.

- Slave disables SPI to ensure data line is released.

(a)

Configuring the MCUs

The method of configuring each MCU for bidirectional data transfer is slightly different, due to the differences in their SPI silicon implementation. Figure 1 shows the hardware implementation. On the 68HC11, the input and output pins must be connected together externally. On the 6805L3, this can be done internally by software, thus requiring only 1 external data I/O pin. The other 6805L3 SPI data pin is now free to be used in any other way.

As the slave select (SS) pins are unused by either MCU, they must be configured as outputs to prevent SPI fault conditions occurring.

The spare 6805L3 data pin (PD3) is used to control the bi-directional data line, thus providing a handshake signal to the 68HC11. The 68HC11's handshake is on the clock line, and is controlled by disabling and enabling its SPI.

# Data transfer and timing

Figure 2 shows details of the handshake sequence. The significant point to note from Figure 2 is that the handshake sequence is implemented purely in software, while the 8-bit data and clocks are generated by the SPI hardware.

To prevent data contention, both during data transfer and during the handshake sequence, both SPIs must operate in wired-or (open drain) mode. On the 6805L3, this is done by setting bit 3 in the miscellaneous register, while on the 68HC11, bit 5 of the SPI control register must be set. The SPI utilised on the 68HC05 family of MCUs does not support this open-drain option and cannot, therefore, be used in this application.

The clock format is: idle low, data output on positive edge and sampled on negative edge. Both SPIs must be configured to operate with the same clock format (see Figure 2). Eight data bits are transferred, at a maximum clock rate of 125 kHz,

which is limited by the 6805L3 SPI. Data transfer is preceded by the handshake sequence, which ensures that both MCUs are in the correct state, and ready to transfer a new byte of data.

The most significant bit of data appears first, on the rising edge of the first clock. Data is latched into both SPI shift registers on the falling edge of the clock. Once the last data bit is latched, the data line is released high. This is necessary to ensure correct operation of the handshake sequence. When the 68HC11 is acting as a transmitter, this state occurs automatically — as a by product of its SPI hardware implementation. However, on completion of data transmission from the 6805L3, the LSB is permanently maintained on the data line, so its driver routine has been designed to ensure that the data line is always restored to the high state.

#### Software routines

A glance at the software listing (see Appendix 1) reveals that the transmit and receive routines for each MCU are essentially the same! The entry and exit conditions of each are as shown in table 1.

On the 6805L3, the X register dictates the operating mode of the transfer routine. This is necessary because the same I/O pin is used for transmitting and receiving data, so its data direction register must be changed appropriately (by the contents of X).

On the 68HC11, separate pins are used for transmitting and receiving data, so their DDR pins are set up once only in the initialisation routine.

There are other important subtle differences. Prior to reception of data, the 6805L3 SPI data register content is irrelevant, while the 68HC11 SPI data register must be loaded with \$FF, to prevent data bus contention. This could occur with the 68HC11, in this application, because data is simultaneously output to and read back on the same external line

Table 1

#### 68HC11:

|        | Transmit<br>ACCA | Receive<br>ACCA |                                                               |

|--------|------------------|-----------------|---------------------------------------------------------------|

| Entry. | Data to send     | \$FF            | X Reg = base address of I/O Register block (normally \$1000). |

| Exit   | Data sent        | Data received   | X Reg = unchanged                                             |

All other registers are unused by the 68HC11 transfer routine.

#### 6805L3:

|       | Transı       | mit   | Receive       |       |  |

|-------|--------------|-------|---------------|-------|--|

|       | ACC          | X Reg | ACC           | X Reg |  |

| Entry | Data to send | \$5   | Don't care    | \$1   |  |

| Exit  | Data sent    | \$D   | Data received | \$D   |  |

during data transfer. Loading \$FF into the 68HC11 data register ensures that this data is replaced by that transmitted from the 6805L3.

Note that, as the 68HC11 is the clock master, it must provide the clock signal, not only when transmitting data, but also when receiving data from the 6805L3. It does this by writing to its SPI data register.

Completion of data transfer is indicated by a single flag bit (SPIF). On the 6805L3, this is bit 7 of the SPI control register, while on the 68HC11, it is bit 7 of the SPI status register. This flag bit is used to indicate completion of either transmission or reception of data.

Flag clearing techniques are quite different for the 68HC11 and 6805L3. On the latter, the SPIF flag is cleared simply by writing '0' to the flag bit. On the 68HC11, a two stage operation is required to clear the SPIF flag; the SPI status register must first be read, with the flag set, followed by an access of the SPI data register.

An examination of the SPI software drivers shows that on completion of a data transmission, the SPI data register is read again. This data should be the same as that transmitted, and provides information on whether data contention or corruption occurred during transfer. This facility could be incorporated in a data validation routine to improve reliability of data transfer.

The key features in this implementation are:

- An orderly start-up sequence to ensure the correct initial synchronisation. As the 6805L3 is the slave, its initialisation routine is not exited until it detects a low on the clock line this will occur only when the 68HC11 gains control of the SPI. Before this happens, all I/O pins are set to inputs, so the clock line will be pulled high by the external resistor.

- A well defined transfer protocol is used. The

master device (i.e. 68HC11) must always

dictate the data transfer direction and the data

stream size must be specified by the currently

selected transmitter, so that the receiver

knows when the last byte has been sent.

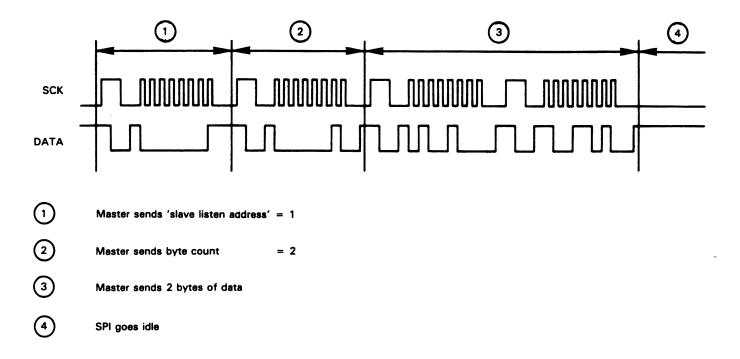

The transfer protocol operates such that after initialisation, the master MCU (68HC11) transmits a control byte to the slave (6805L3). This control byte selects the subsequent data transfer direction and is either a slave listen address or a slave talk address. If it is a slave listen address, then the 6805L3 stays in receive mode. The next byte indicates the total number of bytes to be received, followed by the data stream (see Figure 3).

Once the last byte is transferred, the 6805L3 can await a new control byte, or alternatively it can return to some other task, such as processing the previously received data. Similarly, at this point, the

Figure 3. Master Transmitter - Slave Receiver

master transmitter (68HC11) can return to another task, or send a new control byte.

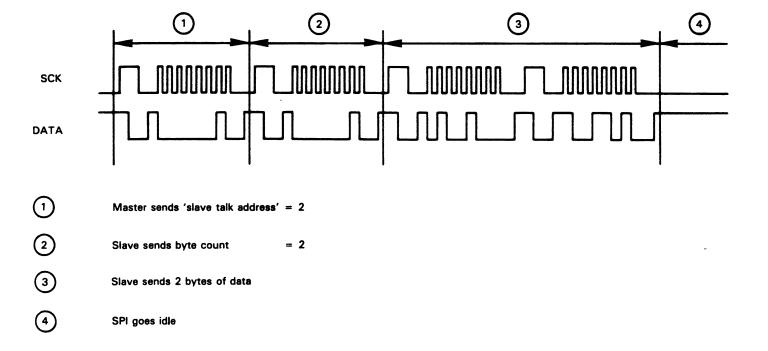

If the control byte now sent is a slave talk address, then the 6805L3 will switch to transmit mode, and the master will switch to receive mode. The 6805L3 will send a byte count, followed by the data stream to the master (see Figure 4).

Note that, once the last byte is transferred in either direction, both processors are free to continue other tasks or attempt a new data transfer. The handshake sequence always ensures synchronisation of data transfer, independent of the response time of either MCU.

#### CONCLUSION

Potential uses for this type of data transfer are in applications which require remote interrogation of an

MCU based system via a minimal number of lines, such as:

- Development and diagnosis of engine management systems

- Smart card and key card security applications

- Instrumentation and data logging equipment.

#### **APPENDIX**

The demonstration programs listed in the following pages simply transfer a string of characters from the 68HC11 to the 6805L3, which converts them to upper case and sends them back again.

The HC11SPI program is listed on pages 6 to 7; the L3SPI program on pages 8 to 10.

Figure 4. Master Receiver - Slave Transmitter

| 1 P<br>2 P<br>3 P<br>4 P                                                                                                    |                                                                                                                  | *******                                                 | ********<br>H                                                                 | **************************************                              | *****  | *******                                                                                                                                                                                                                                         |   |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3 P<br>5 P<br>6 P<br>7 P                                                                                                    |                                                                                                                  | * CLOCK                                                 | LINES. TH                                                                     | TH HANDSHAKE ON SI<br>IS IS NECESSARY AS<br>D BY SLAVE DEVICE       | is HC1 |                                                                                                                                                                                                                                                 |   |

| 8 A A A A A A A A A A A A A A A A A A A                                                                                     | 0008<br>0009<br>0028<br>0029<br>002A<br>0024<br>0025                                                             | PORTD<br>DORD<br>SPCR<br>SPSR<br>SPDR<br>TMSK2<br>TFLG2 | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU                                 | 8<br>9<br>\$28<br>\$29<br>\$24<br>\$24<br>\$25                      |        |                                                                                                                                                                                                                                                 |   |

| 16 A<br>17 A<br>18 A                                                                                                        | 0004<br>0008<br>0010<br>0080<br>0040                                                                             | MISO<br>MOSI<br>SOX<br>SPIF<br>SPE                      | EGN<br>EGN<br>EGN<br>EGN<br>EGN                                               | 4<br>8<br>\$10<br>\$80<br>\$40                                      |        |                                                                                                                                                                                                                                                 |   |

| 24 A 00                                                                                                                     | 02 62632D6469<br>00 0001<br>00 0000                                                                              | TIMCOUNT<br>MSG1                                        | ORG<br>RMB<br>FCB<br>FCC                                                      | \$0<br>1<br>28<br>/bi-directional [                                 |        | NUMBER OF BYTES IN DATA BLOCK<br>Fransfer/                                                                                                                                                                                                      |   |

| 31 A CC<br>32 A CC<br>33 A CC<br>34 A CC                                                                                    | C000<br>00 8E0035<br>03 8D3C<br>05 18CE0001<br>09 8D08<br>0B 18CE0001<br>0F 8D17<br>011 20F2                     | START1                                                  | ORG<br>LDS<br>BSR<br>LDY<br>BSR<br>LDY<br>BSR<br>BRA                          | \$C000<br>#\$35<br>INIT<br>#MSG1<br>SEND<br>#MSG1<br>READ<br>START1 |        | LOAD INTO EVB RAM BUFFALO USES RAM ABOVE THIS Y POINTS TO BEGINNING OF DATA BLOCK TO TRANSFER FRANSMIT BLOCK TO SLAVE, STARTING WITH BYTE COUNT RE-INITIALISE POINTER TO DATA BLOCK AND READ THE BYTES BACK.                                    |   |

| 38 A CCCC<br>39 A A CCCC<br>41 A A A CCCC<br>43 A A A CCCC<br>45 A A A A A CCCC<br>46 A A A A A A A A A A A A A A A A A A A | 122 8020<br>124 5A<br>125 26F6                                                                                   | SEND1                                                   | EQU<br>LDAA<br>BSR<br>LDAA<br>TAB<br>BSR<br>LDAA<br>BSR<br>DECB<br>BNE<br>RTS | #1 XFER , Y XFER XFER SEND1                                         | )<br>  | ENTER WITH Y POINTING AT BYTE COUNT OF DATA BLOC COMMAND SLAVE TO RECEIVE  NOW SEND SLAVE THE BYTE COUNT. BUT 1ST STORE IT IN BYTE COUNTER.  POINT AT NEXT BYTE  AND SEND IT JINTIL ALL DONE                                                    |   |

| 49 A CC<br>50 A CC<br>51 A CC<br>53 A CC<br>54 A CC                                                                         | C028<br>128 8602<br>12A 8025<br>12C 86FF<br>12E 8021<br>130 16<br>131 184700<br>134 1808<br>136 86FF<br>138 8017 | READ1                                                   | EQU<br>LDAA<br>BSR<br>LDAA<br>BSR<br>TAB<br>STAA<br>INY<br>LDAA<br>BSR        | #2 #2 #5FF #\$FF XFER  *Y #\$FF XFER                                | !      | ENTER WITH Y POINTING AT BYTE COUNT OF DATA BLOCK COMMAND SLAVE TO TRANSMIT  NOW READ BYTES BACK FROM SLAVE.  IST BYTE IS BYTE COUNT SO STORE IT IN BYTE COUNTER THEN STORE IT AT BEGINNING OF DATA BLOCK.  SUMP POINTER  THEN CONTINUE TO READ | • |

| 59 A CO3A 18A7OO<br>60 A CO3D 5A<br>61 A CO3E 26F4<br>62 A CO4O 39<br>63 A<br>64 A CO41 CE10OO<br>66 A CO44 8638<br>67 A CO46 A7O9<br>68 A CO48 8676<br>69 A CO4A A728<br>70 A CO4C 8618<br>71 A CO4E A7O8<br>72 A CO5O 39 | * INIT                                | STAA<br>DECB<br>BNE<br>RTS<br>EQU<br>LDX<br>LDAA<br>STAA<br>LDAA<br>STAA<br>RTS                        | .Y READ1  #\$1000 #\$38 DDRD.X #\$76 SPCR.X #\$18 PORTD.X                                              | AND STORE BYTES  UNTIL ALL DONE  ENABLE OUTPUT MODE ON SS.SCK.MOSI, INPUT ON MISO (WITH SS AS OUTPUT, MODE IS DISABLED.) ENABLE SPI AS 125KHZ CLOCK MASTER, WIRED-OR MODE  SET DATA & CLOCK OUTPUT BUFFERS TO LOGIC '1' TO GENERATE ACKNOWLEDGE CLOCK.                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74 A<br>75 A<br>76 A<br>77 A<br>78 A<br>79 A                                                                                                                                                                               |                                       | HANDSHA<br>Entered                                                                                     | TIONAL DATA TRANSFER.<br>KE ON CLOCK & DATA LI<br>WITH DATA IN ACCA, S<br>OW, DATA LINE DETERMI        | INES. *                                                                                                                                                                                                                                                                                                                 |

| 80 A C051 81 A C051 1F0804FC 82 A C055 1D2840 83 A C058 1E0804FC 84 A C05C 1C2840 85 A C05F 1F0804FC 86 A C05F 1F0804FC 86 A C05F 1F2980FC 88 A C069 A62A 89 A C068 39 90 A 91 A 92 A 93 A                                 | * * * * * * * * * * * * * * * * * * * | EQU<br>BRCLR<br>BCLR<br>BRSET<br>BRSET<br>BRCLR<br>STAA<br>BRCLR<br>LDAA<br>RTS<br>ORG \$FF<br>FDB STA | * PORTD,X,#MISO,* SPCR,X,#SPE PORTD,X,#MISO,* SPCR,X,#SPE PORTD,X,#MISO,* SPDR,X SPSR,X,#SPIF,* SPDR,X | 1ST WAIT FOR SLAVE TO RELEASE DATA LINE. SEND ACK ON CLOCK LINE, BY DISABLING SPI WAIT FOR SLAVE TO ACKNOWLEDGE. ENABLE SPI, CLEARING CLOCK LINE. WAIT FOR SLAVE TO RELEASE DATA LINE, THEN START SPI TRANSACTION BY WRITING DATA. NOW WAIT FOR TRANSMISSION COMPLETE FLAG. CLEAR SPIF, AND READ DATA BEFORE RETURNING. |

| ***** TOTAL ERRORS ***** TOTAL WARNINGS                                                                                                                                                                                    | 0 <del></del>                         | 0                                                                                                      |                                                                                                        |                                                                                                                                                                                                                                                                                                                         |

SYMBOL TABLE LISTING

| SYMBOL NAME                                              | SECT              | VALUE                                                                                | SYMBOL NAME                                                                                  | SEC1      | VALUE                                                                        |

|----------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------|

| DDRD INIT MISO MOSI MSG1 PORTD READ READ1 SCK SEND SEND1 | A A A A A A A A A | 0009<br>C041<br>0004<br>0008<br>0001<br>0008<br>C028<br>C034<br>0010<br>C013<br>C01D | SPCR<br>SPDR<br>SPE<br>SPIF<br>SPSR<br>START<br>START1<br>TFLG2<br>TIMCOUNT<br>TMSK2<br>XFER | AAAAAAAAA | 0028<br>002A<br>0040<br>0080<br>0029<br>0005<br>0025<br>0000<br>0024<br>0051 |

| OLINOI                                                   |                   | OOID                                                                                 | 71 LI                                                                                        | _         | COOL                                                                         |

| 12345670                                                                                                                                                                                                                                                  | * BETW                                   | L3SPI<br>SHÅKED BIG<br>EN 6805L3<br>IS CLOCK                                      | 4/9/86 DIRECTIONAL DAS & 68HC11 USI MASTER.                            | ATA TRANSFE | **************************************         | **  *  *  *  *  *  *  *  *  *  *  *  *                                                                      |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|

| 8 P<br>9 A 0000<br>10 A 0003<br>11 A 0004<br>12 A 0007<br>13 A 0008<br>14 A 0009<br>15 A 000C<br>17 A 000D<br>18 A 000E<br>19 A 000F<br>20 A 0010                                                                                                         | MISC<br>TBDAT<br>TBCR<br>SPIDAT<br>SPICR | 88888888888888888888888888888888888888                                            | 0<br>3<br>4<br>7<br>8<br>9<br>\$A<br>\$C<br>\$D<br>\$E<br>\$F<br>\$10  |             |                                                |                                                                                                             |       |

| 18 A 000E 19 A 000F 20 A 0010 21 P 22 A 0001 23 A 0001 24 A 0002 25 A 0003 26 A 0007 28 P 29 A 0020 30 A 0020 31 A 0021 31 A 0021 31 A 0021 32 A 0022 33 A 0080 34 A 0080 35 A 0080 36 A 0080 37 A 0080 37 A 0080 38 A 0080 39 A 0085 AD40 39 A 0085 AD40 | SCK<br>SDA                               | 69<br>69<br>69<br>69<br>69<br>69<br>69<br>69                                      | 0<br>1<br>2<br>3<br>4<br>7                                             | C           | DATA LINE                                      | CLAMP ON D3                                                                                                 |       |

| 29 A 0020<br>30 A 0020 0001<br>31 A 0021 0001<br>32 A 0022 0028                                                                                                                                                                                           | BYTCNT<br>DATLEN<br>DATA                 | ORG<br>RMB<br>RMB<br>RMB                                                          | \$20<br>1<br>1<br>40                                                   | F           | RESERVE E                                      | NOUGH SPACE FOR RECEIVED                                                                                    | DATA. |

| 40 A 0087 A101<br>41 A 0089 2706<br>42 A 0088 A102<br>43 A 0080 271A<br>44 A 008F 20F2                                                                                                                                                                    | START START1                             | ORG<br>EQU<br>BSR<br>CLRA<br>LDX<br>BSR<br>CMP<br>BEQ<br>CMP<br>BEQ<br>BEQ<br>BRA | \$80<br>INIT<br>#1<br>XFER<br>#1<br>READ<br>#2<br>SEND<br>START1       | 1<br>F<br>1 | LST RECEI<br>[F SLAVE<br>READ MORE<br>[F SLAVE | E SPI, AND WAIT FOR HC11 VE COMMAND BYTE REQUESTED TO LISTEN, THEN DATA. REQUESTED TO TALK, THEN TO MASTER. |       |

| 45 A 46 A 0091 47 A 0091 AE01 48 A 0093 AD3E 49 A 0095 B720 50 A 0097 B721 51 A 0099 AE01 52 A 0098 AD3E 53 A 0090 BE20 54 A 009F A020 55 A 00A1 E722 56 A 00A3 3A20 57 A 00A5 2672 58 A 00A7 200                                                         | READ1                                    | EQU<br>LDX<br>BSR<br>STA<br>STA<br>SDX<br>BSR<br>LDX<br>SUB<br>STA<br>DEC<br>BRA  | #1 XFER BYTCNT DATLEN #1 XFER BYTCNT #\$20 DATA.X BYTCNT READ1 START 1 | ,           | ALSO STOR<br>NOW READ                          |                                                                                                             |       |

| 59 A 00A9 61 A 00A9 B621 62 A 00AB B720 63 A 00AD AE05 64 A 00AF AD22 65 A 00B1 BE20 66 A 00B3 E622 67 A 00B5 AE05 68 A 00B7 AD1A 69 A 00B9 3A20 70 A 00BB 26F4 71 A 00BD 20C4 72 A 73 A 00BF | SEND1      | EQU<br>LDA<br>STA<br>LDX<br>BSR<br>LDX<br>LDX<br>LDX<br>BSR<br>DEC<br>BNE<br>BRA | DATLEN BYTCNT #5 XFER BYTCNT DATA, X #5 XFER BYTCNT SEND1 START1                                                                      | GET LENGTH OF DATA AND STORE IT IN BYTE COUNTER.  SEND BYTE COUNT TO MASTER. NOW GET NEXT BYTE TO SEND IN ACC  SEND IT TO MASTER  UNTIL ALL DONE, AND RETURN.                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74 A 00BF A648<br>75 A 00C1 B70A<br>76 A 00C3 A60D<br>77 A 00C5 B703<br>78 A 00C7 A609<br>79 A 00C9 B707<br>80 A 00CB A644                                                                    | INIT       | EQU<br>LDA<br>STA<br>LDA<br>STA<br>LDA<br>STA<br>LDA<br>STA<br>BRSET<br>RTS      | #\$48<br>MISC<br>#\$D<br>PORTD<br>#9<br>DORD<br>#\$44<br>SPICR<br>SOK,PORTD,•                                                         | INHIBIT INT2, ENABLE PORTD OPEN DRAIN.  SET DATA,SS & CLAMP O/P BUFFERS, CLEAR REST.  NOTE: CLAMP ON D3  SELECT SPI CLOCK SLAVE, D2 AS I/P, CLAMP & SS AS O/P. (SS O/P STOPS SPI RESETING)  DISABLE START BIT DETECTION, DATA I/O ON D2, DATA SAMPLED ON -IVE CLOCK, SPI DISABLED.  MUST WAIT FOR MASTER TO GAIN CONTROL OF SPI. |

| 81 A 000D B70F<br>82 A 000F 0203FD<br>83 A 0002 81<br>84 A<br>85 A<br>86 A<br>87 A<br>88 A<br>89 A<br>90 A<br>91 A<br>92 A<br>93 A<br>94 A<br>94 A<br>96 A 0003 0303FD<br>96 A 0006 1703      | ENTRY:     | ENTERED D2 PIN I TX MODE: RX MODE: TX MODE:                                      | IONAL DATA TRANSFER ( WITH SPI DISABLED, D/ /P, CLAMP PIN O/P (H) ACCA=DATA, X=5 ACCA=x , X=1 ACCA=TX DATA, X=\$D ACCA=RX DATA, X=\$D | ATA PIN HIGH®                                                                                                                                                                                                                                                                                                                    |

| 94 A 0003<br>95 A 0003 0303FD<br>96 A 0006 1703<br>97 A 0008 0203FD<br>98 A 0008 B70E<br>99 A 0000 180F<br>100 A 000F BF07<br>101 A                                                           | XFER       | EQU<br>BRCLR<br>BCLR<br>BRSET<br>STA<br>BSET<br>STX                              | SCK.PORTD.* CLAMP.PORTD SCK.PORTD.* SPIDAT SPE.SPICR DORD TRANSFER                                                                    | WAIT FOR MASTER TO ACKNOWLEDGE ON CLOCK LINE. SEND ACKNOWLEDGE TO MASTER. WAIT FOR MASTER TO ENABLE ITS SPI NOW WRITE DATA TO SPI REGISTER, BEFORE ENABLING SPI, AND RELEASING CLAMP CLAMP PIN I/P: DATA EITHER I/P OR O/P. STARTS NOW!                                                                                          |

| 102 A 00E1 A644<br>103 A 00E3 AE0D<br>104 A 00E5 OF0FFD<br>105 A 00E8 B70F<br>106 A 00EA B60E<br>107 A 00EC BF03<br>108 A 00EE BF07<br>109 A 00F0 81                                          | •          | LDA<br>LDX<br>BRCLR<br>STA<br>LDA<br>STX<br>STX<br>RTS                           | #\$44<br>#\$D<br>SPIF,SPICR.*<br>SPICR<br>SPIDAT<br>PORTD<br>DORD                                                                     | PREPARE TO CLEAR SPI FLAG, DISABLE SPI, "AND SEND ACKNOWLEDGE. WAIT FOR DATA TO ARRIVE. DISABLE SPI TO ALLOW DATA PIN TO BE FORCED HIGH READ DATA. FORCE DATA PIN HIGH & RELEASE CLAMP BY MAKING BOTH OUTPUTS.                                                                                                                   |

| 110 A<br>111 A<br>***** TOTAL ERRORS<br>***** TOTAL WARNINGS                                                                                                                                  | 0 (<br>0 ( | END<br>)                                                                         |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                  |

MOTOROLA M6805 X-ASSEMBLER 2.00 SYS:1030.SPI .L3SPI .SA 09/04/86 17:52:15

# SYMBOL TABLE LISTING

| SYMBOL NAME                                                                                                                   | SECT VALUE                                                                                 | SYMBOL NAME                                                                                                                 | SECT VALUE                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| BYTCNT<br>CLAMP<br>DATA<br>DATLEN<br>DORA<br>DORD<br>INIT<br>MISC<br>PORTA<br>PORTID<br>PRESCL<br>READ<br>READI<br>SCK<br>SDA | A 0020 A 0003 A 0022 A 0021 A 0007 A 008F A 000A A 0003 A 0010 A 0091 A 0099 A 0001 A 0002 | SEND<br>SEND1<br>SPE<br>SPICR<br>SPIDAT<br>SPIF<br>SS<br>START1<br>START1<br>TACR<br>TADAT<br>TBCR<br>TBCR<br>TBDAT<br>XFER | A 00A9 A 00B1 A 000F A 000F A 000C A 0083 A 0083 A 0009 A 0008 A 0008 A 0008 A 0008 |

This page intentionally left blank.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 🛞 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Mfax is a trademark of Motorola, Inc.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1-303-675-2140 or 1-800-441-2447

JAPAN: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan. 81-3-5487-8488

Customer Focus Center: 1-800-521-6274

Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE 1-602-244-6609

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

Motorola Fax Back System

- US & Canada ONLY 1-800-774-1848 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

- http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps/